PRODUCTS

UST-SPD-SZJDBH-071

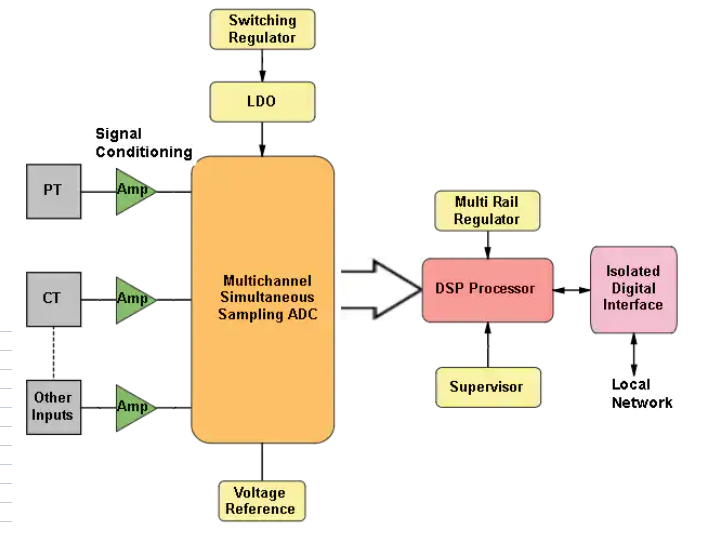

This scheme designs a data acquisition device, which is specially used for the data acquisition of relay protection test instruments.

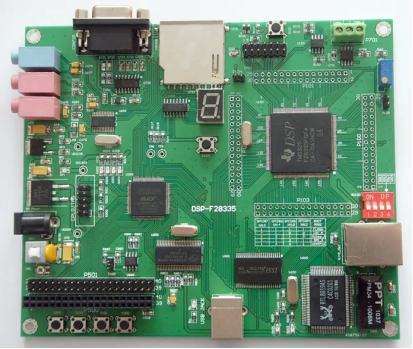

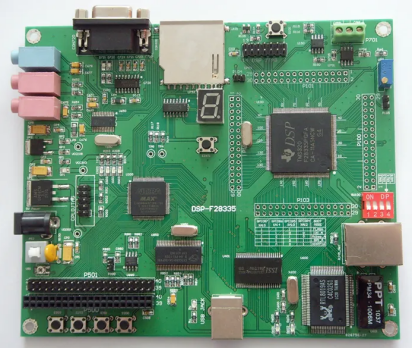

DSP is selected as the core controller of the data acquisition device.

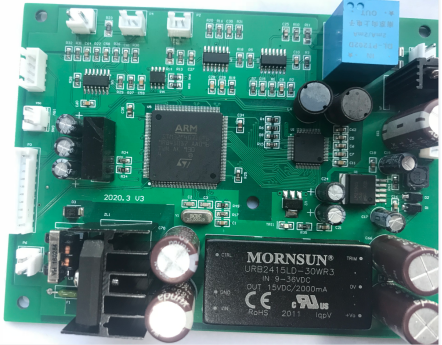

This scheme is composed of voltage and current sampling circuit, signal amplification, low-pass filtering, synchronous signal acquisition and identification, DC sampling, A / D conversion circuit and communication module circuit.

The main control chip DSP is TMS320F28335. Maximum operating frequency of 150 MHz, Harvard structure, 6 independent parallel data and address buses

The 32-bit accumulator, 16 bit hardware multiplier.

AD7502,one of four is selected as the data selector.

ADS8515, single channel ADC, up to 250ksps sampling rate.

USB 2.0 interface,supports 7 in endpoints, 7 out endpoints and a fixed control in / out endpoint.

Isp1581 is internally integrated with serial interface engine (SIE), pie, 8 KB FIFO memory, data transceiver, PLL’s 12 MHz crystal oscillator and 3.3 V voltage regulator.

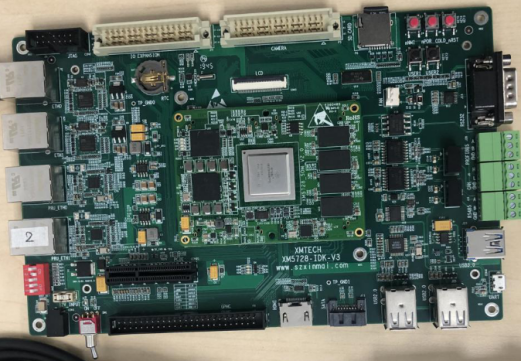

High performance hardware design platform, modular design of CPU and DSP.

The device is equipped with a protective starting element. Only when the protective starting element acts can the positive power supply of the outlet relay be opened.

High speed 40 point sampling, real-time parallel computing..

Fully enclosed case, strong and weak current shall be strictly separated.

Use y - > Δ The phase of CT secondary current at each side of the transformer is transformed and adjusted, and the magnetizing inrush current locking criterion adopts split phase braking.

By using the zero sequence current component, the airdrop can be reliably locked, and the airdrop can act quickly in case of fault.

Products Recommended

- E-mailsales@ustwireless.com

- Phone00852-38449311

- AddressRoom H28, Block EH, 10/F, Golden Bear Industrial Centre, 66-82 Chai Wan Kok Street, Tsuen Wan, Hong Kong