PRODUCTS

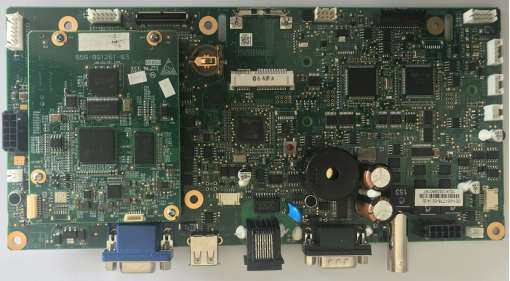

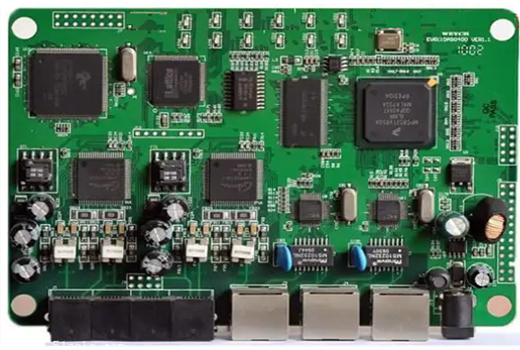

UST-BC018

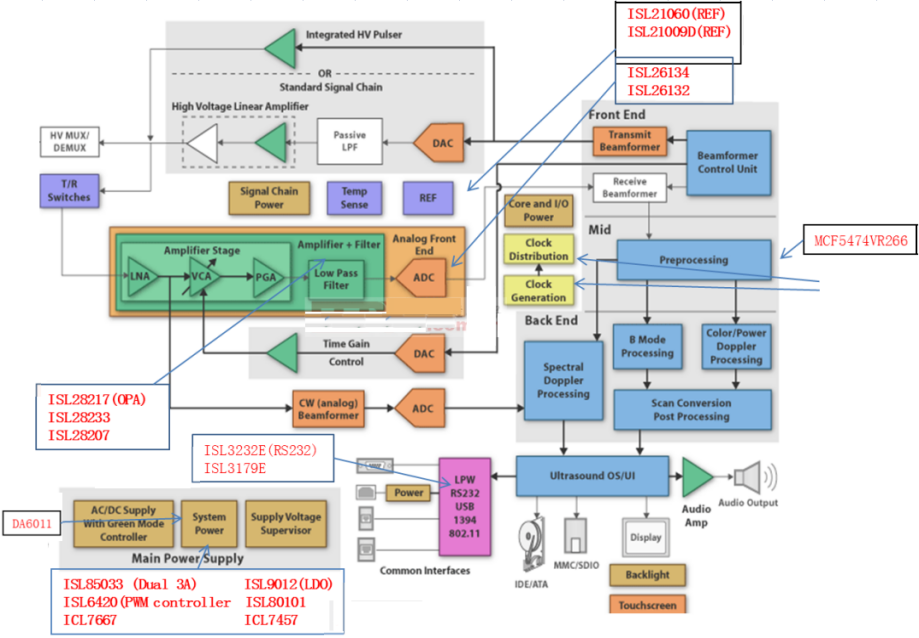

UST-BC018 Scheme master chip MPU;MCF5474VR266.

Limited superscalar V4 ColdFire processor core

Up to 266 MHz peak internal core frequency (410 MIPS [Dhrystone 2.1] @ 266 MHz)

Harvard architecture

2-Kbyte instruction cache

32-Kbyte data cache

Memory Management Unit (MMU)

Separate, 32-entry, fully-associative instruction and data translation lookahead buffers

Floating point unit (FPU)

Double-precision conforms to IEE-754 standard

Eight floating point registers

High performance split address and data transactions

Support for various parking modes

32-bit double data rate (DDR) synchronous DRAM

VREF ISL21060 voltage references,is a low power, high precision voltage references.

LDO ISL9012, a high performance dual LDO,with Low Noise, Low IQ, and High PSRR.

DC TO DC ISL6420 Advanced Single Synchronous Buck Pulse-Width Modulation (PWM) Controller.

RS232 Interface.

USB Interface.

Products Recommended

- E-mailsales@ustwireless.com

- Phone00852-38449311

- AddressRoom H28, Block EH, 10/F, Golden Bear Industrial Centre, 66-82 Chai Wan Kok Street, Tsuen Wan, Hong Kong